# High-level architecture for a low-cost embedded vehicle system

Ignacio López, Rubén Salvador, Jaime Alarcón, and Félix Moreno

SPIE

An intelligent system, modularly designed and requiring limited resources, can automatically detect traffic signals and may be adapted to other applications.

New vehicles from the automotive industry include a growing number of progressively more sophisticated embedded systems, including a variety of Advanced Driver Assistance Systems (ADASs), such as lane departure warning<sup>1</sup> and adaptive cruise control. For both reasons of cost and technology, these innovations draw upon limited resources, leading to highly specific, optimized architectures for each application and platform. The goal remains the development of dependable products capable of real-time environment recognition and decision-making for passenger safety.

The level of intelligence demanded for such systems can only be achieved by adapting high-level cognitive architectures and developing new methods for designing integrated circuits. Algorithm parallelism, for which hardware is especially well-suited, and the current computational power of Field-Programmable Gate Arrays (FPGAs), must be exploited.

With these parameters in mind, we are exploring the possibility of scaling down artificial intelligence techniques (neural networks) and BB1-inspired blackboard architecture<sup>2,3</sup> to effectively use limited resources, initially to detect traffic signals.

FPGA boards allow implementation of intrinsically parallel techniques such as artificial neural networks.<sup>4,5</sup> However, low-cost FPGAs, such as might be used in industrial applications, offer extremely limited resources. We therefore propose a new approach that stresses conceptual and hardware architectural design. We use a low-cost FPGA of the Altera Cyclone family.

Our system is based on image input from a CCD camera installed on the dashboard facing the road. These images are ana-

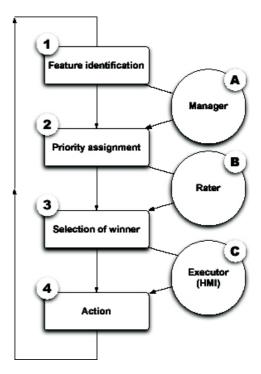

*Figure 1. Phases (1-4) and agents (A-C) of an execution cycle in blackboard architecture. Adaptation of the BB1 blackboard architecture*<sup>2,3</sup>*.*

lyzed for features that may indicate the presence of a traffic signal, such as segments of circumference and right-angled or acute corners. Three neural networks perform this analysis, each specialized in identifying one type of feature. They carry out phase 1 (see Figure 1), with execution coordinated by agent A. The position and number of features is analyzed by programmed functions in phase 2, and assigned a priority level by agent B, the 'rater.' Results are conveyed to the driver through the 'executor' agent, a human-machine interface, labelled C.

The order by which the agents operate, and the data and re-

Continued on next page

## SPIE

## Newsroom

10.1117/2.1xxxxxxxx Page 2/3

sources used in the process, correspond from a conceptual viewpoint to blackboard architecture,<sup>2,3</sup> a well-known type of cognitive architecture developed to facilitate data-sharing in artificial intelligence.

Insufficient resources prevent strict implementation of blackboard architecture with our hardware. A single neural network agent requires virtually all the FPGA. We use at least three agents, and so must either employ several FPGA devices or share a single one. Taking the latter alternative, we have built a single hardware neural network (double layer perceptron) in the FPGA, which we call Generic Neural Network (GNN), shared between all agents. This represents a form of hardware reconfiguration.<sup>6</sup>

The GNN is configured for each agent in runtime. It is loaded with network weights and agent biases that are stored in memory after being previously calculated off-line with Matlab. Weights of unused neurons are turned to zero. Reconfiguration and execution times are sufficiently short to allow new frame processing from the camera every 40ms (PAL rate).

The hardware architecture for GNN has been optimized. Each layer includes its own control logic. A layer of n neurons can perform the corresponding n operations in parallel due to independent access to the memories of each neuron. To prevent precision losses, over- and underflows, the the data path has been dimensioned.

#### Conclusions

Designing intelligent embedded systems for the automotive industry requires adapting high-level techniques to limited resources. We have optimized usage by sharing the same hardware for all system elements to create a generic, runtime configurable hardware neural network. System parts and operation employ a blackboard architecture.

These system architectures provide a high degree of modularity, necessary for consistent scalability. System functionality, currently traffic signal detection, can be enhanced by adding new data (weights and biases) to memory. In the near term, the system will include pedestrian detection. Modularity also allows scaling. The system is currently implemented on a single Altera Cyclone FPGA. However, the same architecture could be easily deployed on several FPGAs, or over hybrid, FPGA-DSP-Analog boards.

The functional and platform scalability we describe will enable future applications with increased intelligent capabilities, and an optimal performance/cost tradeoff. Many such applications require advanced perception algorithms and sensory fusion, as well as distributed sensing and action, for which blackboard architecture is particularly well suited.

#### **Author Information**

#### Ignacio López

Autonomous Systems Laboratory, ASLab Universidad Politécnica de Madrid, UPM Madrid, Spain

Ignacio López has devoted his career to systems engineering and cognitive architectures, applied to the automotive indsutry, including methodologies for calculating pollutant emission inventories and the design and development of embedded systems.

#### Rubén Salvador, Jaime Alarcón, and Félix Moreno

Centro de Electrónica Industrial, CEI Universidad Politécnica de Madrid, UPM Madrid, Spain

Rubén Salvador, with a MSc in Electronic Engineering from Universidad de Alcalá (2004) and BSc in Telecommunication Engineering (UPM, 2001), is currently finishing a master's degree in industrial electronics as part of his PhD in electronic engineering (UPM). His research interests include conceiving and designing high-performance reconfigurable and adaptable systems, hardware embedded cognitive architectures, and digital signal processing systems.

Jaime Alarcón Celis, received his bachelor's degree in electrical and mechanical engineering and a master'sdegree in engineering from UPM, where he is currently completing his PhD. He also holds a master's degree in computer science from the Instituto Tecnológico y de Estudios Superiores de Monterrey. He served as Professor and head of the Electronics and Control Department of Tecnológico de Monterrey (Toluca Campus). His research interests are neural networks, parallelism, and real time systems.

Félix Moreno is Assistant Professor of Electronics Engineering at the ETSII-UPM. He received his PhD in telecommunication engineering from UPM. He is coordinator of the Advanced Driver Assistance System for Urban Project Environments (ASISTEN-TUR), TRA2004-07441-C03-03/AUT), with the support of the Spanish Ministry of Science, under the National R&D Plan, through which the work presented here has been developed. He has extensive experience in embedded system design for the automotive and aeronautical sectors.

Continued on next page

## Newsroom

#### References

1. J. Alarcón, R. Salvador, F. Moreno, and I. López, A new Real-Time Hardware Architecture for Pood Line Tracking Using a Particle Filter, pp. 726–741, 2006

chitecture for Road Line Tracking Using a Particle Filter, pp. 736–741, 2006 2. M. Wolverton and L. Brownston, *BB1 v3.2 Manual.*, Tech. Rep. KSL 94-XX, Dept.

of Computer Science, Stanford University, March 1994

3. B. Hayes-Roth, K. Pfleger, P. Lalanda, P. Morignot, and M. Balabanovic, A Domain-Specific Software Architecture for Adaptive Intelligent Systems, IEEE Trans-

actions on Software Engineering 21 (4), pp. 288–301, 1995 4. Y. Taright and M. Hubin, FPGA implementation of a multilayer perceptron

neural network using VHDL, vol. 2, 1998

5. J. J. Blake, L. P. Maguire, T. M. McGinnity, and L. J. McDaid, Using Xilinx FPGAs to implement neural networks and fuzzy systems, May 1997

6. Y. E. Krasteva, E. de la Torre, and T. Riesgo, *Partial Reconfiguration for Core Reallocation and Flexible Communications*, July 2006